Linux 自带 AR8035 驱动,但是很多人不知道。这里给出一个简单方便的方法,给 QCA9558/QCA9557/AR9342/AR9344/AR7141/AR7161 添加 AR8035 支持。

此方法直接使用 ag71xx 驱动,且不需添加驱动,更不用移植 ag7240/ag934x/arths_gmac。Linux 内核中 AR8035 的 PHY 驱动名叫做 at803x,位于 drivers/net/phy/at803x.c

修改方法如下:

(所有改动均在 OpenWrt 代码目录)

1. target/linux/ar71xx/config-3.X (X 依据Linux内核版本而定)

在里面添加一行

CONFIG_AT803X_PHY=y这样能确保 at803x 驱动被编译进内核

2. target/linux/ar71xx/files/arch/mips/ath79/mach-XXXX.c (需要添加 AR8035 支持的文件)

在开头部分添加 at803x 的头文件包含语句

#include <linux/platform_data/phy-at803x.h>

在第一个函数前面添加以下两个全局静态变量:

第一个是对 AR803X 设置 txdelay rxdelay。AR934X 跟 AR7141/AR7161 的设置方法不同。

AR7141/AR7161设置如下:

static struct at803x_platform_data mi124_ar8035_data = {

.enable_rgmii_tx_delay = 1,

};

AR934X/QCA955X设置如下:

static struct at803x_platform_data mi124_ar8035_data = {

.enable_rgmii_rx_delay = 1,

.fixup_rgmii_tx_delay = 1,

};

第二个是在注册 eth 设备时向 ag71xx 驱动传入的设置

static struct mdio_board_info mi124_mdio0_info[] = {

{

.bus_id = "ag71xx-mdio.0",

.phy_addr = 0,

.platform_data = &mi124_ar8035_data,

},

};

.phy_addr = 0 指的是指定使用 MDIO 地址为 0 的 PHY,这个需要根据实际情况(在PCB上的bootstrap pin)来设置

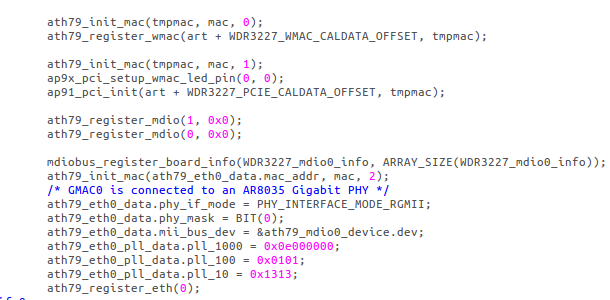

修改代码中eth注册代码如下,确保只注册eth0

ath79_register_mdio(1, 0x0);

ath79_register_mdio(0, 0x0);

mdiobus_register_board_info(mi124_mdio0_info, ARRAY_SIZE(mi124_mdio0_info));

ath79_setup_ar934x_eth_cfg(AR934X_ETH_CFG_RGMII_GMAC0 | AR934X_ETH_CFG_SW_ONLY_MODE);

/* GMAC0 is connected to an AR8035 Gigabit PHY */

ath79_eth0_data.phy_if_mode = PHY_INTERFACE_MODE_RGMII;

ath79_eth0_data.phy_mask = BIT(0);

ath79_eth0_data.mii_bus_dev = &ath79_mdio0_device.dev;

ath79_eth0_pll_data.pll_1000 = 0x0e000000;

ath79_eth0_pll_data.pll_100 = 0x0101;

ath79_eth0_pll_data.pll_10 = 0x1313;

ath79_register_eth(0);

这里面最重要的内容为3个pll值,这些值配合 at803x 的 txdelay 跟 rxdelay 能保证AR8035正常使用。上面代码中三个 pll 值是给 AR934X使用的。

如果使用 AR7141/AR7161,请使用下面的 pll 数值:

ath79_eth0_pll_data.pll_1000 = 0x00110000;

ath79_eth0_pll_data.pll_100 = 0x0001099;

ath79_eth0_pll_data.pll_10 = 0x00991099;

如果使用 QCA9558/QCA9557,请使用下面的 pll 数值:

ath79_eth0_pll_data.pll_1000 = 0x96000000;

ath79_eth0_pll_data.pll_100 = 0x80000101;

ath79_eth0_pll_data.pll_10 = 0x80001313;

注意:

对于 AR934X,有些板子的 AR8035 并没有使用 PHY Addr. 0,此时请把 ath79_eth0_data.phy_mask = BIT(0); 的 BIT(0)从0到15依次试一次。同时要修改上面的 .phy_addr 的值

楼主遇到一个板子,QCA9558 的,使用的 PHY Addr 是 7。。。。。。

以上方法添加的 AR8035 支持能够保证良好的兼容性以及可移植性。

上述方法中 txdelay/rxdelay 设置与 pll 的设置参考了Atheros LSDK 中 U-Boot (AR934X) 和 redboot (AR7161) 代码中的设置。

QCA9558 的 txdelay/rxdelay 设置与 pll 值来源于逆向分析。

QCA9563 没遇到对应的板子,故没有对应的 txdelay/rxdelay 设置与 pll 值。AR7242 也是如此。

AR7242 + AR8021 因为没人愿意借楼主板子来测试,因此无解。

OpenWrt ar71xx 添加原生 AR8035 支持的方法 (AR934X/AR7161/QCA9558)

http://www.right.com.cn/forum/thread-168504-1-1.html

评论